#### MIPI CSI-2/DSI D-PHY ReDriver

#### **Features**

- MIPI D-PHY 1.2 Specification Compliant

- Supports 4 lanes at 2.5Gbps in D-PHY

- Supports ULPS and LP power states and sub-mW in shutdown

- Supports MIPI DSI Bi-directional LP mode

- Programmable and pin adjustable on Receiver Equalization and transmitter edge rate

- Programmable Output swing and Pre-emphasis levels

- Industrial temperature range: -40 °C to 85 °C

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

- https://www.diodes.com/quality/product-definitions/

- Packaging (Pb-free & Green):

- 28-contact, TQFN (ZH), 5.5 x 3.5 mm

### **Description**

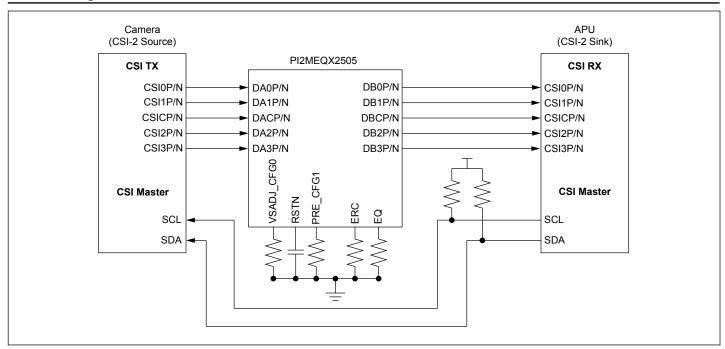

The PI2MEQX2505 is a low power, high performance 2.5Gbps four lanes data and clock MIPI D-PHY ReDriver<sup>™</sup> designed specifically for MIPI D-PHY 1.2 protocol.

The device provides programmable equalization, output swing and pre-emphasis to optimize performance over a variety of physical mediums by reducing Inter-Symbol Interference. PI2MEQX2505 supports MIPI D-PHY 1.2 standard with  $100\Omega$ differential CML data I/O between CSI-2 Source and CSI-2 Sink, over cable, or to extend the signals across other distant data pathways on the user's platform. It also supports pin adjustable on receiver equalization and edge rate on transmitter rise and fall time.

PI2MEQX2505 is optimized for mobile applications, and contains activity detection circuitry on the D-PHY Link interface that can transit into a lower power mode when in ULPS and LP states.

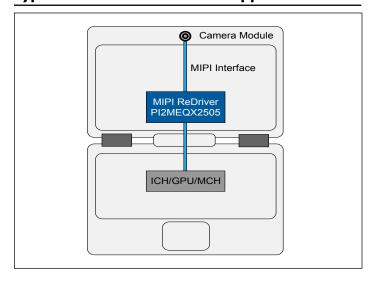

### Typical MIPI Re-Driver in NB Application

### **Applications**

- Notebook PC

- Clamshell

- **Tablets**

- Camera

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

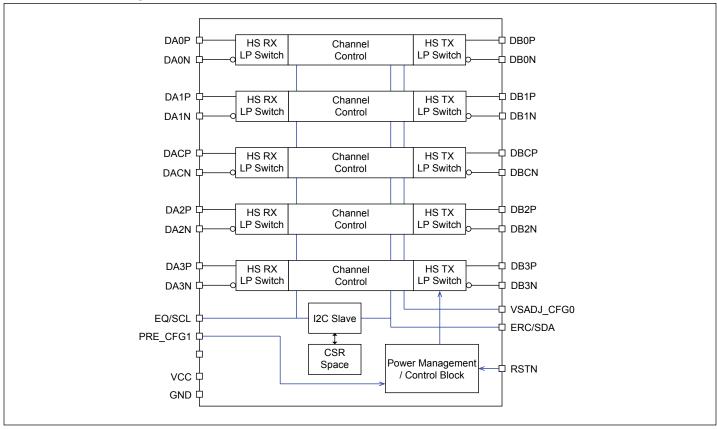

## **Block Diagram**

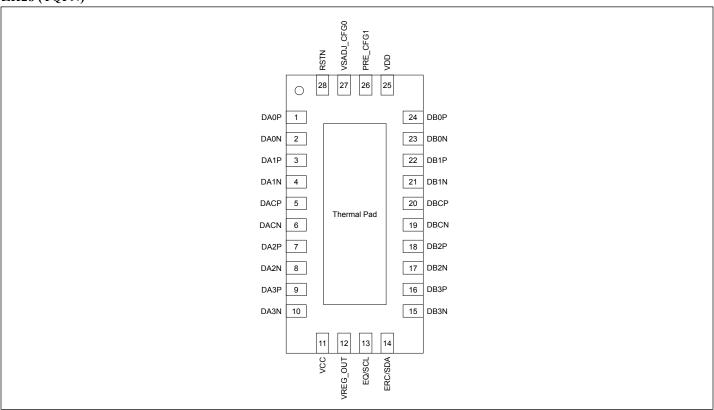

## **Pin Configuration**

ZH28 (TQFN)

## **Pin Description**

| Pin# | Pin Name | Туре                  | Description                                                                                                           |

|------|----------|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| 1    | DA0P     | $100\Omega$ Differen- | CSI-2/DSI Lane 0 Differential positive Input. Supports DSI LP Backchannel. If unused, this pin should be tied to GND. |

| 2    | DA0N     | tial<br>Input         | CSI-2/DSI Lane 0 Differential negative Input. Supports DSI LP Backchannel. If unused, this pin should be tied to GND. |

| 3    | DA1P     | $100\Omega$ Differen- | CSI-2/DSI Lane 1 Differential positive Input. If unused, this pin should be tied to GND.                              |

| 4    | DA1N     | tial<br>Input         | CSI-2/DSI Lane 1 Differential negative input. If unused, this pin should be tied to GND.                              |

| 5    | DACP     | 100Ω<br>Differen-     | CSI-2/DSI Differential Clock positive Input                                                                           |

| 6    | DACN     | tial<br>Input         | CSI-2/DSI Differential Clock negative Input                                                                           |

## **Pin Description Cont.**

| Pin# | Pin Name | Tyj                 | pe               | Description                                                                                                                                                   |

|------|----------|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | DA2P     | 100Ω<br>Differen-   |                  | CSI-2/DSI Lane 2 Differential positive Input. If unused, this pin should be tied to GND.                                                                      |

| 8    | DA2N     | tial<br>Input       |                  | CSI-2/DSI Lane 2 Differential negative Input. If unused, this pin should be tied to GND.                                                                      |

| 9    | DA3P     | 100Ω<br>Differen-   |                  | CSI-2/DSI Lane 3 Differential positive Input. If unused, this pin should be tied to GND.                                                                      |

| 10   | DA3N     | tial<br>Input       |                  | CSI-2/DSI Lane 3 Differential negative Input. If unused, this pin should be tied to GND.                                                                      |

| 11   | VCC      | Power               |                  | 1.8V (±10%) Supply.                                                                                                                                           |

| 12   | VREG_OUT | Power               |                  | 1.2V Regulator Output. Requires a 0.1 μF capacitor to GND.                                                                                                    |

|      |          | , .                 | Pullup/          | RX Equalization Select. Pin state sampled on rising edge of RSTN. This pin also functions as I2C SCL pin.                                                     |

| 13   | EQ/SCL   | (2.11)              | Pull-<br>down    | $EQ/SCL = V_{IL}$ : Equalization = 3dB                                                                                                                        |

|      |          | (3-level)           | (100K)           | $EQ/SCL = V_{IM}$ : Equalization = 6dB                                                                                                                        |

|      |          |                     |                  | EQ/SCL = V <sub>IH</sub> : Equalization = 9dB                                                                                                                 |

| 14   | ERC/SDA  | I/O                 | Pullup/<br>Pull- | Edge Rate Control for DB[4:0]P/N High speed transmitter rise and fall time. Pin state sampled on rising edge of RSTN. This pin also functions as I2C SDA pin. |

| 14   | ERC/SDA  | (3-level)           | down             | $ERC/SDA = V_{IL}$ : Edge rate = 200ps                                                                                                                        |

|      |          |                     | (100K)           | $ERC/SDA = V_{IM}$ : Edge rate = 150ps                                                                                                                        |

|      |          |                     |                  | ERC/SDA = V <sub>IH</sub> : Edge rate = 250ps                                                                                                                 |

| 15   | DB3N     | 100Ω<br>Differen-   |                  | CSI-2/DSI Lane 3 Differential negative Output. If unused, this pin should be left unconnected.                                                                |

| 16   | DB3P     | tial<br>Output      |                  | CSI-2/DSI Lane 3 Differential positive Output. If unused, this pin should be left unconnected.                                                                |

| 17   | DB2N     | 100Ω<br>Differen-   |                  | CSI-2/DSI Lane 2 Differential negative Output. If unused, this pin should be left unconnected.                                                                |

| 18   | DB2P     | tial<br>Output      |                  | CSI-2/DSI Lane 2 Differential positive Output. If unused, this pin should be left unconnected.                                                                |

| 19   | DBCN     | 100Ω<br>- Differen- |                  | CSI-2/DSI Differential Clock negative Output                                                                                                                  |

| 20   | DBCP     | tial Output         |                  | CSI-2/DSI Differential Clock positive Output                                                                                                                  |

| 21   | DB1N     | 100Ω<br>Differen-   |                  | CSI-2/DSI Lane 1 Differential negative Output. If unused, this pin should be left unconnected.                                                                |

| 22   | DB1P     | tial<br>Output      |                  | CSI-2/DSI Lane 1 Differential positive Output. If unused, this pin should be left unconnected.                                                                |

# Pin Description Cont.

| Pin#       | Pin Name   | Туре              |                                    | Description                                                                                                                                                                                                                                                                                              |

|------------|------------|-------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | DB0N       | 100Ω<br>Differen- |                                    | CSI-2/DSI Lane 0 Differential negative Output. Supports DSI LP Back channel. If unused, this pin should be left unconnected.                                                                                                                                                                             |

| 24         | DB0P       | tial<br>Output    |                                    | CSI-2/DSI Lane 0 Differential positive Output. Supports DSI LP Back channel. If unused, this pin should be left unconnected.                                                                                                                                                                             |

| 25         | VDD        | Power             |                                    | This pin must be connected to the VREG_OUT pin through at least a 10-mil trace and a 0.1 $\mu F$ capacitor to ground.                                                                                                                                                                                    |

| 26         | PRE_CFG1   | I<br>(3-level)    | Pullup/<br>Pull-<br>down<br>(100K) | Controls DPHY TX HS pre-emphasis level and the LP TX rise and fall times. Pin state is sampled on the rising edge of RSTN. $PRE\_CFG1 = V_{IL} : Pre\text{-emphasis level} = 0 \ dB$ $PRE\_CFG1 = V_{IM} : Pre\text{-emphasis level} = 1 \ dB$ $PRE\_CFG1 = V_{IH} : Pre\text{-emphasis level} = 3 \ dB$ |

| 27         | VSADJ_CFG0 | I<br>(3-level)    | Pullup/<br>Pull-<br>down<br>(100K) | Controls output voltage swing for DB HS transmitters and the LP TX rise and fall times. Pin state is sampled on the rising edge of RSTN. $VSADJ\_CFG0 = V_{IL} : Swing = 225 \ mV \\ VSADJ\_CFG0 = V_{IM} : Swing = 250 \ mV \\ VSADJ\_CFG0 = V_{IH} : Swing = 275 \ mV$                                 |

| 28         | RSTN       | I                 |                                    | Reset, active low. When low, all internal CSR are reset to default and PI2MEQX2505 is placed in low power state.                                                                                                                                                                                         |

| Center Pad | GND        | GND               |                                    | Ground.                                                                                                                                                                                                                                                                                                  |

## **Maximum Ratings**

(Above which useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature65°C to +150°C                 |

|---------------------------------------------------|

| Supply Voltage to Ground Potential0.3V to +2.175V |

| Voltage Range                                     |

| D-PHY Lane I/O Differential Voltage0.3V to +1.4V  |

| RSTN0.3V to +2.175V                               |

| All Other Terminals                               |

| Max Junction Temperature                          |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

**ESD Rating**

| Symbol                   | Parameter        | Conditions                                                                     | Value | Units |

|--------------------------|------------------|--------------------------------------------------------------------------------|-------|-------|

| V <sub>(ESD)</sub> Elect | Elekaratik diede | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | 2000  | V     |

|                          |                  | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | 1000  | V     |

**Recommended Operating Conditions**

| Symbol          | Parameter                      | Conditions | Min. | Тур. | Max. | Units |

|-----------------|--------------------------------|------------|------|------|------|-------|

| V <sub>CC</sub> | Supply voltage                 |            | 1.62 | 1.8  | 1.98 | V     |

| $T_{A}$         | Operating free-air temperature |            | -40  |      | 85   | °C    |

#### **Electrical Characteristics, Power Supply**

Over operating free-air temperature range (unless otherwise noted)

| Symbol   | Parameter                                              | Conditions                                                                            | Min. | Тур. | Max. | Units |

|----------|--------------------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|-------|

| PACTIVE1 | Power under normal operation for 4 data lanes + clock. | D-PHY Lanes at 2.5 Gbps;<br>V <sub>CC</sub> supply stable, V <sub>CC</sub> =<br>1.8 V |      | 135  | 200  | mW    |

| PACTIVE2 | Power under normal operation for 2 data lanes + clock. | D-PHY Lanes 2.5 Gbps; $V_{CC}$ supply stable, $V_{CC} = 1.8 \text{ V}$                |      | 80   | 120  | mW    |

| P_LP11   | LP11 Power                                             | All D-PHY lanes in LP11; $V_{CC}$ supply stable; $V_{CC}$ = 1.8 V                     |      | 2    | 5    | mW    |

| P_STB    | Standby mode power                                     | RSTN held in asserted state (low); $V_{CC}$ supply stable; $V_{CC}$ = 1.8 V           |      | 0.02 | 0.2  | mW    |

| P_ULPS   | ULPS mode power                                        | IC stay in ULPS mode; $V_{CC}$ supply stable; $V_{CC} = 1.8 \text{ V}$                |      | 2    | 5    | mW    |

#### **Electrical Characteristics**

Over operating free-air temperature range (unless otherwise noted)

| Symbol                  | Parameter                                                  | Conditions                                                      | Min.                 | Typ.               | Max.                 | Units |

|-------------------------|------------------------------------------------------------|-----------------------------------------------------------------|----------------------|--------------------|----------------------|-------|

| Standard IO             | (RSTN, ERC, EQ, CFG[1:0])                                  |                                                                 | `                    |                    |                      |       |

| $ m V_{IL}$             | Low-level control signal input voltage                     |                                                                 | 0                    |                    | 0.14xV <sub>CC</sub> | V     |

| $V_{IM}$                | Mid-level control signal input voltage                     |                                                                 | 0.45xV <sub>CC</sub> | V <sub>CC</sub> /2 | 0.55xV <sub>CC</sub> | V     |

| $ m V_{IH}$             | High-level control signal input voltage                    |                                                                 | 0.86xV <sub>CC</sub> |                    | VCC                  | V     |

| $V_{\mathrm{F}}$        | Floating Voltage                                           | V <sub>IN</sub> = High Impedance                                |                      | $V_{CC}/2$         |                      | V     |

| $V_{OL}$                | Low level output voltage (open-drain). ERC (SDA) only      | At I <sub>OL</sub> max.                                         |                      |                    | 0.2xV <sub>CC</sub>  | V     |

| $I_{OL}$                | Low Level Output Current                                   |                                                                 |                      |                    | 3                    | mA    |

| $I_{IH}$                | High level input current                                   |                                                                 |                      |                    | ±36                  | μΑ    |

| $ m I_{IL}$             | Low level input current                                    |                                                                 |                      |                    | ±36                  | μΑ    |

| $R_{PU}$                | Internal pull-up resistance                                |                                                                 |                      | 100                |                      | kΩ    |

| $R_{PD}$                | Internal pull-down resistance                              |                                                                 |                      | 100                |                      | kΩ    |

| R <sub>(RSTN)</sub>     | RSTN control input pullup resistor                         |                                                                 |                      | 300                |                      | kΩ    |

| SCL, SDA                |                                                            |                                                                 |                      |                    |                      |       |

| $V_{\mathrm{IL}}$       | Low-level I2C signal input voltage                         |                                                                 |                      |                    | 0.3xV <sub>CC</sub>  | V     |

| $ m V_{IH}$             | High-level I2C signal input voltage                        |                                                                 | 0.7xV <sub>CC</sub>  |                    |                      | V     |

| MIPI D-PHY              | HS Receiver Interface (DA0P/N,                             | DA1P/N, DA2P/N, DA3P/N,                                         | DACP/N)              |                    |                      |       |

| V <sub>(CM-RX_DC)</sub> | Differential Input Common-<br>mode voltage HS Receive mode | $V_{\text{(CM-RX)}} = (V_{\text{A x P}} + V_{\text{A x}}$ N) /2 | 70                   |                    | 330                  | mV    |

| 137                     | HS Receiver input differential voltage                     | $ V_{ID}  =  V_{A \times P} - V_{A \times N} $ <1.5 Gbps        | 70                   |                    |                      | mV    |

| V <sub>ID</sub>         |                                                            | $ V_{ID}  =  V_{A \times P} - V_{A \times N} $<br>>1.5 Gbps     | 40                   |                    |                      | mV    |

| V <sub>IH(HS)</sub>     | Single-ended input high voltage                            |                                                                 |                      |                    | 460                  | mV    |

| V <sub>IL(HS)</sub>     | Single-ended input low voltage                             |                                                                 | -40                  |                    |                      | mV    |

| R <sub>(DIFF-HS)</sub>  | Differential input impedance                               |                                                                 | 75                   | 100                | 125                  | Ω     |

| V <sub>(RXEQ0)</sub>    | Rx EQ gain when EQ/SCL pin ≤ V <sub>IL</sub>               |                                                                 |                      | 3                  |                      | dB    |

| V <sub>(RXEQ1)</sub>    | Rx EQ gain when EQ/SCL pin = V <sub>IM</sub>               | At 1250 MHz                                                     |                      | 6                  |                      | dB    |

| V <sub>(RXEQ2)</sub>    | Rx EQ gain when EQ/SCL pin ≥ V <sub>IH</sub>               | At 1250 MHz                                                     |                      | 9                  |                      | dB    |

### **Electrical Characteristics Cont.**

| Symbol                        | Parameter                                                                    | Conditions                                                                                                                                                 | Min.       | Тур.  | Max. | Units |

|-------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|------|-------|

| MIPI D-PHY                    | Y LP Receiver Interface (DA0P/N                                              | , DA1P/N, DA2P/N, DA3P/N, D                                                                                                                                | ACP/N, DB  | 0P/N) | ·    | '     |

| V <sub>(LPIH)</sub>           | LP Logic 1 Input Voltage                                                     |                                                                                                                                                            | 880        |       |      | mV    |

| V <sub>(LPIL)</sub>           | LP Logic 0 Input voltage                                                     |                                                                                                                                                            |            |       | 550  | mV    |

| V <sub>(HYST)</sub>           | LP Input Hysteresis                                                          |                                                                                                                                                            | 25         |       |      | mV    |

| MIPI D-PHY                    | Y HS Transmitter Interface (DB0)                                             | P/N, DB1P/N, DB2P/N, DB3P/N                                                                                                                                | N, DBCP/N) |       |      |       |

| V <sub>(CMTX)</sub>           | HS Transmit static common-<br>mode voltage, VSADJ_CFG0 =<br>VIL              | $V_{(CMTX)} = (V_{(BP)} + V_{(BN)}) / 2$                                                                                                                   | 150        | 200   | 250  | mV    |

| $ \Delta V_{(CMTX)} $ $(1,0)$ | VCMTX mismatch when output is differential-1 or differential-0               | $\Delta V_{(CMTX) (1,0)} = (V_{(CMTX)} (1) - V_{(CMTX) (0)}) / 2$                                                                                          |            |       | 5    | mV    |

| $ V_{\mathrm{OD(VD0)}} $      | HS Transmit differential voltage, VSADJ_CFG0 = VIL                           | $ V_{\mathrm{OD}}  =  V_{(\mathrm{DP})} - V_{(\mathrm{DN})} $                                                                                              | 140        | 200   | 270  | mV    |

| $ \Delta V_{\mathrm{OD}} $    | $V_{OD}$ mismatch when output is differential-1 or differential-0            | $\Delta V_{\rm OD} =  \Delta V_{\rm O(D1)}  -  \Delta V_{\rm O(D0)} $                                                                                      |            |       | 14   | mV    |

| V <sub>OH(HS)</sub>           | HS Output high voltage for non-transition bit                                | $CFG0 \ge V_{IH} HS Pre = 3 dB$                                                                                                                            |            |       | 430  | mV    |

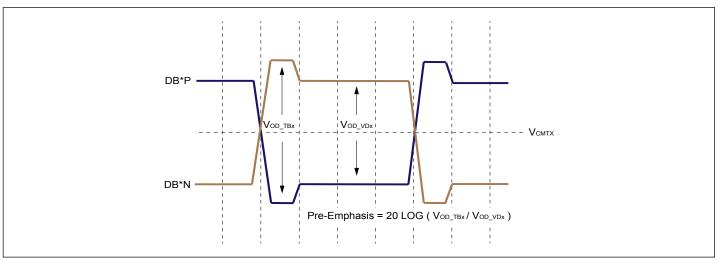

| V <sub>(PRE1)</sub>           | Pre-emphasis Level for HSTX_<br>PRE_CFG1 = VIM                               | $\begin{aligned} & \text{PRE} = 20 \text{ x LOG } \left( V_{\text{OD(TBx)}} / \right. \\ & V_{\text{OD(VDX)}} \right), \text{See Figure 1.} \end{aligned}$ |            | 1     |      | dB    |

| V <sub>(PRE2)</sub>           | Pre-emphasis level for HSTX_<br>PRE_CFG1 = VIH                               | $\begin{aligned} & \text{PRE} = 20 \text{ x LOG } (V_{\text{OD(TBx)}} / \\ & V_{\text{OD(VDX)}}), \text{ See Figure 1.} \end{aligned}$                     |            | 3     |      | dB    |

| R <sub>pd(HS)</sub>           | Pull down resistor when RSTN = 0 V                                           |                                                                                                                                                            |            | 300   |      | kΩ    |

| LP Mode Sw                    | itch Interface                                                               |                                                                                                                                                            |            |       |      |       |

| R <sub>ON_LP</sub>            | I <sub>ON</sub> = -8 mA, DA0P/N,<br>DA1P/N, DA2P/N, DA3P/N,<br>DCP/N = 1.2 V | V <sub>CC</sub> = 1.8 V                                                                                                                                    |            | 30    | 60   | Ω     |

| ΔR <sub>ON_LP</sub>           | I <sub>ON</sub> = -8 mA, DA0P/N,<br>DA1P/N, DA2P/N, DA3P/N,<br>DCP/N = 1.2 V | V <sub>CC</sub> = 1.8 V                                                                                                                                    |            | 0.1   | 0.5  | Ω     |

| C <sub>ON</sub>               |                                                                              | V <sub>CC</sub> = 1.8 V                                                                                                                                    |            | 7     |      | pF    |

| -3db BW                       |                                                                              | V <sub>CC</sub> = 1.8 V; DC bias = 0 V                                                                                                                     |            | 800   |      | MHz   |

Figure 1. DPHY HS TX Pre-emphasis

**Timing Requirements**

| Symbol                | Parameter                                                                                   | Conditions | Min. | Тур. | Max. | Units |

|-----------------------|---------------------------------------------------------------------------------------------|------------|------|------|------|-------|

| I2C (ERC (S           | DA), EQ (SCL))                                                                              |            |      |      |      |       |

| t <sub>HD;STA</sub>   | Hold Time (repeated) START condition. After this period, the first clock pulse is generated |            | 4    |      |      | μs    |

| $t_{LOW}$             | Low period of SCL clock                                                                     |            | 4.7  |      |      | μs    |

| t <sub>HIGH</sub>     | High period of SCL clock                                                                    |            | 4    |      |      | μs    |

| t <sub>SU;STA</sub>   | Setup time for a repeated START condition                                                   |            | 4.7  |      |      | μs    |

| t <sub>HD;DAT</sub>   | Data hold time                                                                              |            | 5    |      |      | μs    |

| t <sub>SU;DAT</sub>   | Data setup time                                                                             |            | 4    |      |      | μs    |

| t <sub>SU;STO</sub>   | Setup time for STOP condition                                                               |            | 4    |      |      | μs    |

| $t_{\mathrm{BUF}}$    | Bus free time between a STOP and START condition                                            |            | 4.7  |      |      | μs    |

| RSTN                  |                                                                                             |            |      |      |      |       |

| t <sub>D1</sub>       | V <sub>CC</sub> stable before de-assertion of RSTN                                          |            | 100  |      |      | μs    |

| t <sub>SU2</sub>      | Setup of VSADJ_CFG0, PRE_<br>CFG1, EQ and ERC pin before<br>de-assertion of RSTN            |            | 0    |      |      | μs    |

| t <sub>h2</sub>       | Hold of VSADJ_CFG0, PRE_<br>CFG1, EQ and ERC pin after<br>de-assertion of RSTN              |            | 250  |      |      | μs    |

| t <sub>VCC_RAMP</sub> | V <sub>CC</sub> supply ramp requirements                                                    |            | 0.2  |      | 100  | ms    |

| Delay Time            | for HS Mode                                                                                 |            |      |      |      |       |

| t <sub>HSPD</sub>     | Propagation delay from DA to DB. In HS mode                                                 |            |      | 1    |      | ns    |

## **Switching Characteristics**

Over operating free-air temperature range (unless otherwise noted)

| Symbol                            | Parameter                                       | Conditions                               | Min.       | Typ.(1) | Max. | Units  |

|-----------------------------------|-------------------------------------------------|------------------------------------------|------------|---------|------|--------|

| I2C (ERC (SE                      | OA), EQ (SCL))                                  |                                          |            |         |      |        |

| F <sub>(SCL)</sub>                | I2C Clock Frequency                             |                                          |            |         | 100  | kHz    |

| t <sub>F_I2C</sub>                | Fall time of both SDA and SCL signals           | Load of 350 pF with 2-K pullup resistor. |            |         | 300  | ns     |

| t <sub>R_I2C</sub>                | Rise Time of both SDA and SCL signals           | Measure at 30% - 70%                     |            |         | 1000 | ns     |

| D-PHY Link                        |                                                 |                                          |            |         |      |        |

| F <sub>(BR)</sub>                 | Bit Rate                                        |                                          |            |         | 2.5  | Gbps   |

| F <sub>(HSCLK)</sub>              | HS Clock Input range                            |                                          | 100        |         | 1250 | MHz    |

| MIPI D-PHY                        | HS Receiver Interface (DACP/N                   | , DA0P/N, DA1P/N, DA2P/N, I              | DA3P/N)    |         |      |        |

| 437                               | Common-mode Interface be-                       |                                          |            |         | 100  | mV     |

| $\Delta V_{(CMRX\_HF)}$           | yond 450 MHz                                    | >1.5 GHz                                 |            |         | 50   | mV     |

| $\Delta V_{(CMRX\_LF)}$           | Common-mode interference 50<br>MHz – 450 MHz    |                                          | -50        |         | 50   | mV     |

| MIPI D-PHY                        | HS Transmitter Interface (DBC)                  | P/N, DB0P/N, DB1P/N, DB2P/               | N, DB3P/N) | )       |      |        |

| $\Delta V_{(CMTX\_HF)}$           | Common-level variations above 450 MHz           |                                          |            |         | 15   | mVrms  |

| $\Delta V_{(CMTX\_LF)}$           | Common-level variation between 50 MHz – 450 MHz |                                          |            |         | 25   | mVpeak |

|                                   |                                                 | Datarate ≤ 1 Gbps                        |            |         | 0.3  | UI     |

|                                   | 20% - 80% rise time and fall                    | Datarate > 1 Gbps and ≤ 1.5<br>Gbps      |            |         | 0.35 | UI     |

| t <sub>R</sub> and t <sub>F</sub> | time                                            | Datarate > 1.5 Gbps                      |            |         | 0.4  | UI     |

|                                   |                                                 | Datarate ≤ 1.5 Gbps                      | 100        |         |      | ps     |

|                                   |                                                 | Datarate > 1.5 Gbps                      | 50         |         |      | ps     |

| D-PHY LP R                        | eceiver Interface (DACP/N, DA0F                 | P/N, DA1P/N, DA2P/N, DA3P/I              | N, DB0P/N) |         |      |        |

| e <sub>SPIKE</sub>                | Input Pulse rejection                           |                                          |            |         | 300  | V ps   |

| t <sub>MIN(RX)</sub>              | Minimum pulse width response                    |                                          | 20         |         |      | ns     |

| V <sub>(INT)</sub>                | Peak interference amplitude                     |                                          |            |         | 200  | mV     |

| F <sub>(INT)</sub>                | Interference Frequency                          |                                          | 450        |         |      | MHz    |

| MIPI D-PHY                        | LP Transmitter Interface (DBC)                  | P/N, DB0P/N, DB1P/N, DB2P/               | N, DB3P/N) | )       |      |        |

| $t_{REOT}$                        | 30% - 85% rise time and fall time               | Measured at end of HS transmission.      |            |         | 35   | ns     |

#### Note:

1. All typical values are at  $V_{CC}$  = 1.8V, and  $T_A$  = 25°C.

### **Detailed Description**

#### Overview

The PI2MEQX2505 is a one to four lane and clock MIPI D-PHY ReDriver<sup>™</sup> that regenerates the D-PHY signaling. The device complies with MIPI D-PHY 1.2 standard and can be used in either a MIPI CSI-2 or MIPI DSI application at datarates of up to 2.5 Gbps in D-PHY.

The device compensates for PCB, connector, and cable related frequency loss and switching related loss to provide the optimum electrical performance from a CSI2/DSI source to sink. The PI2MEQX2505 D-PHY inputs feature configurable equalizers.

The PI2MEQX2505 output swing and edge rate can be adjusted by changing the state of the VSADJ\_CFG0 pin and ERC pin respectively. The PI2MEQX2505 is optimized for mobile applications, and contains activity detection circuitry on the D-PHY Link interface that can transition into a lower power mode when in ULPS and LP states.

The device is characterized for an extended operational temperature range from -40°C to 85°C.

## **Functional Block Diagram**

### **Feature Description**

### **HS Receive Equalization**

The PI2MEQX2505 supports three levels of receive equalization to compensate for ISI loss in the channel. These three levels are 3 dB, 6 dB, and 9 dB at 1250Mhz. The equalization level used by the PI2MEQX2505 is determined by the state of the EQ/SCL pin at the rising edge of RSTN. If necessary, the receiver equalization level can also be set through writing to the RXEQ register via the local I2C interface.

Table 1. EQ/SCL Pin Function

| EQ/SCL Pin             | HS Rx Equalization |

|------------------------|--------------------|

| $\leq$ V <sub>IL</sub> | 3 dB               |

| $V_{IM}$               | 6 dB               |

| ≥ V <sub>IH</sub>      | 9 dB               |

### **HS TX Edge Rate Control**

#### Table 2. HS TX Edge Rate Control

| ERC/SDA Pin            | HS Rise/Fall Times |

|------------------------|--------------------|

| $\leq$ V <sub>IL</sub> | 200 ps typical     |

| $V_{IM}$               | 150 ps typical     |

| ≥ V <sub>IH</sub>      | 250 ps typical     |

#### **I2C Slave Address**

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 (W/R) |

|-------|-------|-------|-------|-------|-------|-------|-------------|

| 1     | 1     | 0     | 1     | 1     | 0     | 0     | 0/1         |

## **Register Map**

| Address | Register                           | Туре       | Bit 7                                            | Bit 6                                | Bit 5                  | Bit 4                  | Bit 3        | Bit 2        | Bit 1  | Bit 0 |

|---------|------------------------------------|------------|--------------------------------------------------|--------------------------------------|------------------------|------------------------|--------------|--------------|--------|-------|

| 00h     | Device ID                          | Read       |                                                  | Device ID (PI2MEQX2505): (reset valu |                        |                        | ue: 0000010  | 1b)          |        |       |

| 01h     | Version ID                         | Read       | Version ID (Version 0): (reset value: 00000000b) |                                      |                        |                        |              |              |        |       |

| 02h     | EQ                                 | Read/Write | Res                                              | Reserved (reset value: 0000b) EQ <3> |                        |                        | EQ <2>       | EQ <1>       | EQ <0> |       |

| 03h     | ERC                                | Read/Write | Reserved (reset value: 00000b)                   |                                      |                        | ERC <2>                | ERC <1>      | ERC <0>      |        |       |

| 04h     | Reserved                           | Read       | Reserved (reset value: 00001000b)                |                                      |                        |                        |              |              |        |       |

| 05h     | Output Pre-<br>emphasis &<br>Swing | Read/Write |                                                  |                                      | PREEMP<br>LEVEL<br><1> | PREEMP<br>LEVEL<br><0> | VSADJ<br><1> | VSADJ<br><0> |        |       |

## Register Setting for EQ/ERC/PRE\_CFG1/VSADJ\_CFG0

| EQ<3:0><br>(Register 02h<3:0>) | EQ Gain at 500MHz | EQ Gain at 1250MHz |

|--------------------------------|-------------------|--------------------|

| 0000                           | 0dB               | 0dB                |

| 0010                           | 2dB               | 3dB                |

| 0110                           | 4dB               | 6dB                |

| 1011                           | 6dB               | 9dB                |

| Others                         | Reserved          | Reserved           |

| ERC<2:0><br>(Register 03h<2:0>) | Edge Rate Control |

|---------------------------------|-------------------|

| 001                             | 250ps             |

| 011                             | 200ps             |

| 111                             | 150ps             |

| Others                          | Reserved          |

| PREEMP LEVEL<1:0> (Register 05h<3:2>) | Pre-emphasis Level |

|---------------------------------------|--------------------|

| 00                                    | 0dB                |

| 01                                    | 1dB                |

| 11                                    | 3dB                |

| Others                                | Reserved           |

| VSADJ<1:0><br>Register 05h<1:0> | Output Voltage Swing |

|---------------------------------|----------------------|

| 00                              | 200mV                |

| 01                              | 225mV                |

| 10                              | 250mV                |

| 11                              | 275mV                |

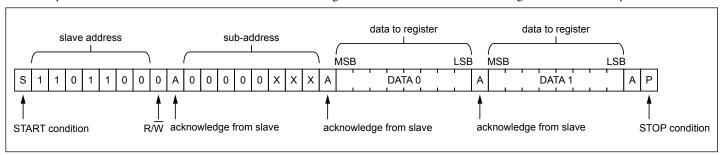

#### **Bus Transaction**

#### Writing to the Registers

Data is transmitted to the PI2MEQX2505 by sending the device address and setting the least significant bit to a logic 0. The register sub-address byte is sent after the address and determines which register will receive the data following the sub-address byte.

Figure 2. Write to Register

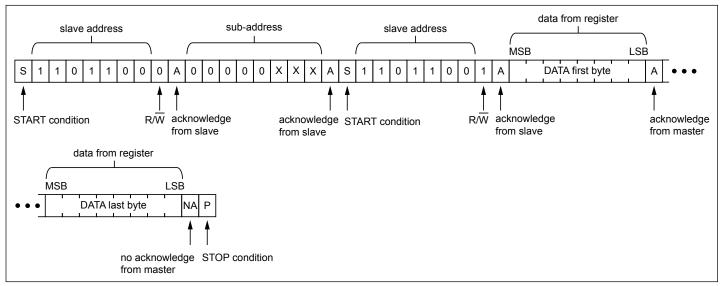

### Reading the Register

In order to read data from the PI2MEQX2505, the bus master must first send the PI2MEQX2505 address with the least significant bit set to a logic 0. The sub-address byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again, but this time the lease significant bit is set to a logic 1. Data from the register defined by the sub-address byte will then be sent by the PI2MEQX2505. Data is clocked into the register on the falling edge of the acknowledge clock pulse.

Figure 3. Read from Register

## **Part Marking**

28-TQFN (ZH)

Z: Die Rev

YY: Date Code (Year)

WW: Date Code (Workweek)

1st X: Assembly Code 2nd X: Fab Code

Bar above 2nd "X" means Cu wire

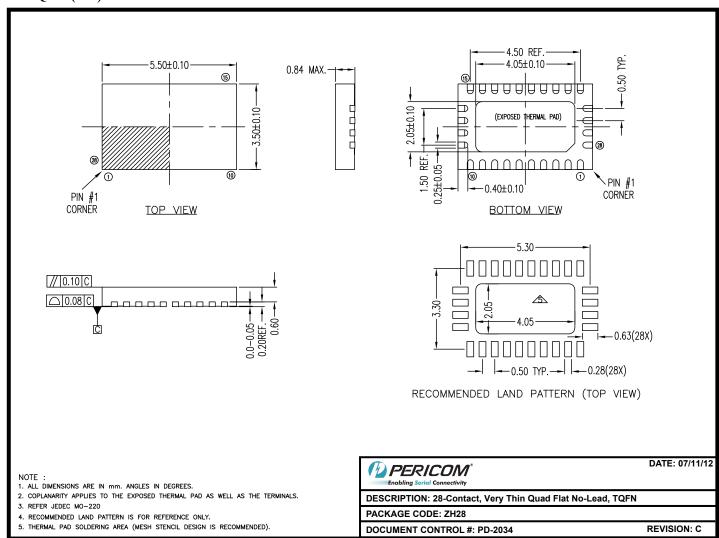

# **Packaging Mechanical**

#### 28-TQFN (ZH)

12-0419

#### For latest package information:

See http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/.

### **Ordering Information**

| Ordering Number | Package Code | Package Description                            |

|-----------------|--------------|------------------------------------------------|

| PI2MEQX2505ZHEX | ZH           | 28-contact, Very Thin Quad Flat No-Lead (TQFN) |

#### Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

- 4. E = Pb-free and Green

- 5. X suffix = Tape/Reel

#### IMPORTANT NOTICE

- 1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2022 Diodes Incorporated

www.diodes.com